Xilinx ISE

14.7- 软件大小:0.05 MB

- 更新时间:2019-12-04

- 星级指数:

- 软件平台:电脑版

- 软件语言:简体中文

- 系统类型:支持32/64位

- 下载次数:279

- 安全监测:[无病毒, 正式版, 无插件]

- 操作系统:WinXP/2000/vista/Win7/Win8/Win10

软件介绍

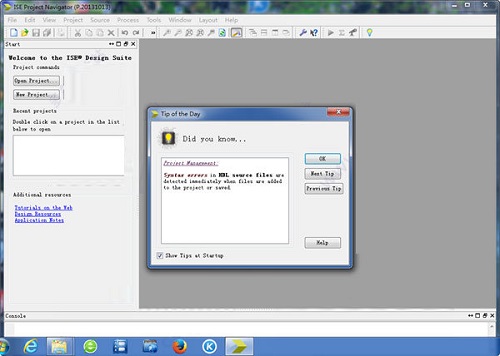

Xilinx ISE官方版是一款非常不错的电子设计套件,Xilinx ISE官方版也是目前的最新版本,全面支持win8和win8.1系统。Xilinx ISE为设计流程的每一步都提供了直观的生产力增强工具,包括设计输入、仿真、综合、布局布线、生成BIT文件、配置以及在线调试等,功能非常强大。除了功能完整,使用方便外,它的设计性能也非常好,是FPGA的必备的设计工具。

Xilinx ISE官方版是一款非常不错的电子设计套件,Xilinx ISE官方版也是目前的最新版本,全面支持win8和win8.1系统。Xilinx ISE为设计流程的每一步都提供了直观的生产力增强工具,包括设计输入、仿真、综合、布局布线、生成BIT文件、配置以及在线调试等,功能非常强大。除了功能完整,使用方便外,它的设计性能也非常好,是FPGA的必备的设计工具。

功能介绍

ISE的主要功能包括设计输入、综合、仿真、实现和下载,涵盖了可编程逻辑器件开发的全过程,从功能上讲,完成CPLD/FPGA的设计流程无需借助任何第三方EDA软件。

1、图形或文本输入(Design Entry)

图形或文本输入包括原理图、状态机、波形图、硬件描述语言(HDL),是工程设计的第一步,ISE集成的设计工具主要包括HDL编辑器(HDL Editor)、状态机编辑器(StateCAD)、原理图编辑器(ECS)、IP核生成器(CoreGenerator)和测试激励生成器(HDL Bencher)等。

常用的设计输入方法是硬件描述语言(HDL)和原理图设计输入方法。原理图输入是一种常用的基本的输入方法,其是利用元件库的图形符号和连接线在ISE软件的图形编辑器中作出设计原理图,ISE中设置了具有各种电路元件的元件库,包括各种门电路、触发器、锁存器、计数器、各种中规模电路、各种功能较强的宏功能块等用户只要点击这些器件就能调入图形编辑器中。这种方法的优点是直观、便于理解、元件库资源丰富。但是在大型设计中,这种方法的可维护性差,不利于模块建设与重用。更主要的缺点是:当所选用芯片升级换代后,所有的原理图都要作相应的改动。故在ISE软件中一般不利用此种方法。

为了克服原理图输入方法的缺点,目前在大型工程设计中,在ISE软件中常用的设计方法是HDL设计输入法,其中影响最为广泛的HDL语言是VHDL和Verilog HDL。它们的共同优点是利于由顶向下设计,利于模块的划分与复用,可移植性好,通用性强,设计不因芯片的工艺和结构的变化而变化,更利于向ASIC的移植,故在ISE软件中推荐使用HDL设计输入法。

波形输入及状态机输入方法是两种最常用的辅助设计输入方法,使用波形输入法时,只要绘制出激励波形的输出波形,ISE软件就能自动地根据响应关系进行设计;而使用状态机输入时,只需设计者画出状态转移图,ISE软件就能生成相应的HDL代码或者原理图,使用十分方便。其中ISE工具包中的StateCAD就能完成状态机输入的功能。但是需要指出的是,后两种设计方法只能在某些特殊情况下缓解设计者的工作量,并不适合所有的设计。

2、综合(Synthesis)

综合是将行为和功能层次表达的电子系统转化为低层次模块的组合。一般来说,综合是针对VHDL来说的,即将VHDL描述的模型、算法、行为和功能描述转换为FPGA/CPLD基本结构相对应的网表文件,即构成对应的映射关系。

在Xilinx ISE中,综合工具主要有Synplicity公司的Synplify/Synplify Pro,Synopsys公司的FPGA Compiler II/ Express, Exemplar Logic公司的LeonardoSpectrum和Xilinx ISE中的XST等,它们是指将HDL语言、原理图等设计输入翻译成由与、或、非门,RAM,寄存器等基本逻辑单元组成的逻辑连接(网表),并根据目标与要求优化所形成的逻辑连接,输出edf和edn等文件,供CPLD/FPGA厂家的布局布线器进行实现。

软件特色

软件图集

相关软件推荐

软件更新

芝麻时钟37.6MB|2024-11-06

直接下载

Chandler电脑版34MB|2024-11-06

直接下载

浩辰CAD看图王电脑版88.84MB|2024-11-06

直接下载

浩辰CAD看图王4.9MB|2024-11-06

直接下载

搜狗拼音输入法149.82MB|2024-11-06

直接下载

搜狗输入法149.82MB|2024-11-06

直接下载

搜狗拼音输入法电脑版149.82MB|2024-11-06

直接下载

搜狗拼音输入法Win版149.82MB|2024-11-06

直接下载

搜狗拼音输入法客户端149.82MB|2024-11-06

直接下载